В связи с растущей потребностью наращивания производительности и снижения энергопотребления серверов, а также довольно радужной перспективой применения в этой области процессоров с архитектурой ARM, в особенности когда они получат 64-битную адресацию памяти, компания ARM пополнила портфель интеллектуальной собственности новыми разработками, которые будут способствовать расширению сферы применения её SoC в сетевых инфраструктурах и серверах.

В связи с растущей потребностью наращивания производительности и снижения энергопотребления серверов, а также довольно радужной перспективой применения в этой области процессоров с архитектурой ARM, в особенности когда они получат 64-битную адресацию памяти, компания ARM пополнила портфель интеллектуальной собственности новыми разработками, которые будут способствовать расширению сферы применения её SoC в сетевых инфраструктурах и серверах.

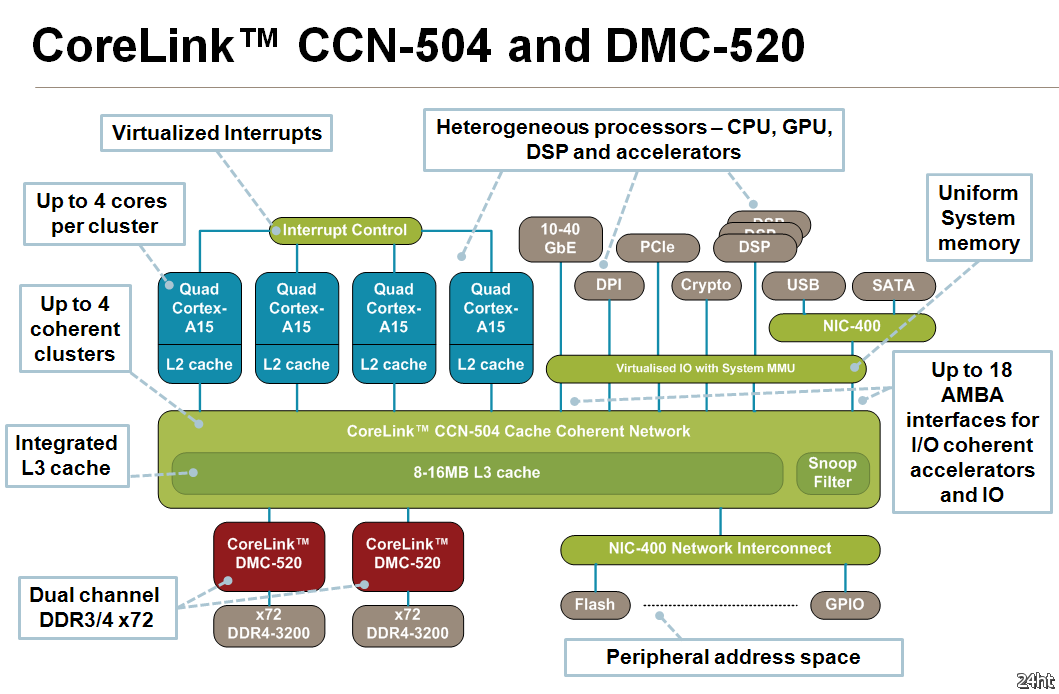

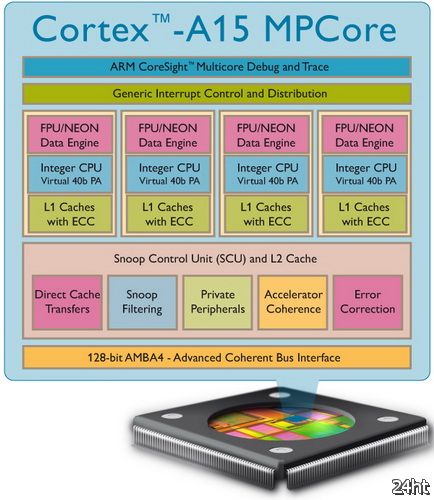

Компания представила сетевую платформу CoreLink CCN-504, которая позволяет объединить на одном кристалле до 4 процессоров Cortex A15 (ARMv7), предоставляя до 16 связанных ядер CPU, а также поддерживает будущие чипы с набором 64-битных инструкций ARMv8. Но даже современные процессоры Cortex-A15 уже обладают рядом важных для серверной отрасли возможностей, включая полную аппаратную виртуализацию, технологию Large Physical Address Extensions, позволяющую адресовать до 1 Тбайт памяти, а также коррекцию ошибок ECC для повышения отказоустойчивости системы.

Процессоры, обладающие собственной кеш-памятью L1 и L2, получают в рамках данной платформы и разделённую кеш-память L3 объёмом от 8 до 16 Мбайт. Наличие фильтра наблюдения позволяет устранить избыточные запросы к каждому из процессоров для согласования данных их кеш-памяти. Система также обладает последовательной кеш-когерентной системной шиной с пропускной способностью до 1 Тбита, что позволяет инженерам создавать сложные многоядерные системы на процессорах ARM.

CoreLink CCN-504 является частью системного решения, продвигаемого ARM и включающего также следующие компоненты:

контроллер динамической памяти DMC-520;

— блок управления системной памяти MMU-400 для виртуализации адресного пространства ввода-вывода;

— контроллер GIC-400 для управления и распределения процессорных прерываний;

— сетевое соединение NIC-400 для поддержки периферийных устройств и систем.

Представленный ARM новый контроллер динамической памяти ARM CoreLink DMC-520 разработан и оптимизирован для работы с CoreLink CCN-504. Он предоставляет широкополосный интерфейс к разделённой внешней DRAM-памяти стандартов DDR3, DDR3L и DDR4.

CoreLink CCN-504 является первым членом семейства продуктов и обеспечивает согласованность гетерогенных ядер и мульти-кластерных систем CPU/GPU, позволяя каждому процессору в системе получать доступ к кешу другого процессора. Данный подход снижает потребность в доступе к внешней памяти, повышая производительность и сохраняя энергию, что является ключевыми принципами систем в рамках идеологии ARM big.LITTLE.

Вместе с началом программы лицензирования CoreLink CCN-504 компания сообщила о том, что лицензии на использование технологии уже получили LSI, выпускающая логику для накопителей, сетевых устройств и других клиентских вычислительных устройств, и Calxeda, поставщик систем на чипе для серверного рынка. Причём последняя уже создала на базе лицензированной технологии ARM CoreLink следующее поколение своих продуктов, рассчитанных на применение в вычислительных центрах и способных, по заявлению компании, оказать сильное воздействие на индустрию.

По мнению ARM, появление данных решений сыграет ключевую роль в развитии высокопроизводительных и многоядерных систем в течение ближайших 10—15 лет, когда потребляемый и обрабатываемый объём данных будет экспоненциально возрастать. Выход продуктов от партнёров компании, использующих платформу ARM CoreLink CCN-504, ожидается в следующем году.

Нет комментарий